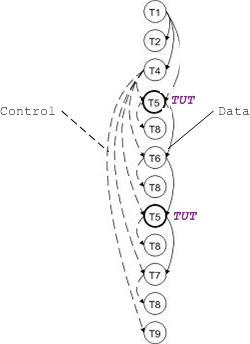

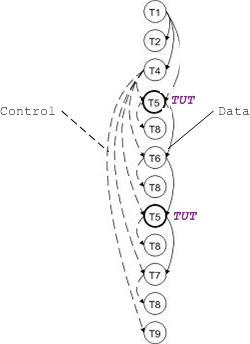

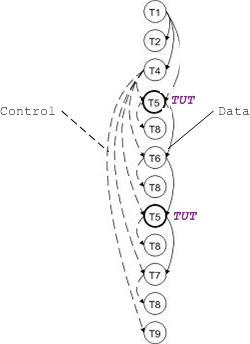

- Test sequence T1 T2 T4 T5 T8 T6 T8 T5 T8 T7 T8 T9 wrt TUT = T5 for the ATM System is used in this example.

- Derive the DDG graph (allowing node repetition) from the SDG graph based on the test sequence:

- Mark the dependencies affecting the TUT by traversing backwards from the TUT to the start state:

- Remove the unmarked dependencies to obtain the DIP:

- The construction of DIP is implemented in the DDG class in file ddg.cpp of the DDG module.

Details of the algorithm can be found in Panitee's thesis. More examples can be found in the test log (testDDG).

Home