# A summary of the 680X0's instruction types (excluding floating-point instructions).

| Instruction type | Opcode                                                                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data transfer    | EXG<br>MOVE<br>SWAP                                                        | Exchange (swap) contents of two registers  Move (copy) data unchanged from source to destination  Swap left and right halves of register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Data processing  | ABCD ADD AND AS.v CLR DIV EOR EXT LS.v MUL NBCD NEG NOT OR ROx SBCD SUB    | Add decimal (BCD) numbers with carry (extend) flag Add binary (two's-complement) numbers Bitwise logical AND Arithmetic shift left $(x = L)$ or right $(x = R)$ with sign extensi Clear operand by resetting all bits to 0 Divide binary numbers Bitwise logical EXCLUSIVE OR Extend the sign bit of subword to fill register Logical shift left $(x = L)$ or right $(x = R)$ Multiply binary numbers Negate decimal number (subtract with carry from zero) Negate binary number (subtract from zero) Bitwise logical complement Bitwise logical OR Rotate left $(x = L)$ or right $(x = R)$ Subtract decimal (BCD) numbers Subtract binary (two's-complement) numbers                                                                                        |

| Program control  | Bcc<br>BRA<br>BSR<br>CMP<br>DBcc<br>JMP<br>JSR<br>NOP<br>RTS<br>Scc<br>TST | Branch relative to PC if specified condition cc is true Branch unconditionally, relative to PC Call (branch to) subroutine at address relative to PC; save PC st:     (return address) in stack Compare two operand values and set flags based on result Loop instruction: Test condition cc and perform no operation if     condition is true; otherwise, decrement specified register and     branch to specified address Branch unconditionally to specified address Call (jump to) subroutine at specified address; save PC state     (return address) in stack No operation, but instruction execution continues Return from subroutine Set operand to 1s (0s) if condition cc is true (false) Test an operand by comparing it to zero and setting flags |

### SOME INSTRUCTIONS OF 68000

| (Address)<br>(Quick) | Transfer of Data  MOVE.size <s>,<d> MOVEA.size <s>,<d> MOVEQ.size <s>,<d></d></s></d></s></d></s> | $\begin{array}{ccc}  &  \leftarrow  & ( \\  &  \leftarrow  & ( \\  &  \leftarrow  & ( \\  &  \leftarrow  \\  &  \\  & $ | Pestrictions<br>$\neq$ Ai)<br>= Ai) (size $\neq$ B)<br>= Imm) ( $\langle d \rangle \neq$ Ai) (size $\neq$ B   W)                      |

|----------------------|---------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

|                      | SWAP Di<br>EXG Xi, Xj                                                                             | $Di(31:16) \leftrightarrow Di(15:0)$<br>$Xi(31:00) \leftrightarrow Xj(31:0)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ·                                                                                                                                     |

| •                    | Addition ADD.size <s>,<d> ADDA.size <s>,<d> ADDI.size <s>,<d></d></s></d></s></d></s>             | <d> ← <d> + <s><br/><d> ← <d> + <s><br/><d> ← <d> + <s></s></d></d></s></d></d></s></d></d>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | $( \neq Ai) (    = Di)$<br>$( = Ai) (size \neq B)$<br>$( = Imm) ( \neq Ai)$                                                           |

|                      | Subtraction                                                                                       | Same as ADD, but w                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | rith keyword SUB                                                                                                                      |

| <del>-</del>         | Multiplication<br>MULU <s>, Di<br/>MULS <s>, Di</s></s>                                           | $Di(31:00) \leftarrow Di(15:0)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | operands are words) 00) * <s></s>                                                                                                     |

| ·                    | Division DIVU <s>, Di DIVS <s>, Di</s></s>                                                        | $Di(31:00) \leftarrow Di(31:0)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | $(\langle s \rangle \neq Ai)$                                                                                                         |

|                      | Other CLR.size <d> NEG.size <d></d></d>                                                           | <d> ← 0<br/><d> ← 2's C of <d></d></d></d>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ( <d>≠ Ai)<br/>(<d>≠ Ai)</d></d>                                                                                                      |

| (Immediate)          | ANDI.size <s>,<d>ANDI.size <s>,<d></d></s></d></s>                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | $( \neq Ai) (    = Di)$<br>$( = Imm) ( \neq Ai)$                                                                                      |

| (Immediate)          | OR.size <s>,<d>ORI.size <s>,<d></d></s></d></s>                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | $( \neq Ai) (    = Di)$<br>$( = Imm) ( \neq Ai)$                                                                                      |

| (Immediate)          | EOR.size <s>,<d> EORI.size <s>,<d></d></s></d></s>                                                | <d> $<$ d> $<$ d> $<$ d> $<$ s> $<$ d> $<$ d> $<$ s> $<$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | $(\langle s \rangle = Di)$ $(\langle d \rangle \neq Ai)$<br>$(\langle s \rangle = Imm)$ $(\langle d \rangle \neq Ai)$ $(size \neq W)$ |

|                      | NOT.size <d></d>                                                                                  | <d> ← <d>′</d></d>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ( <d>≠ Ai)</d>                                                                                                                        |

# Transfer of Control

Bcc <relative address or label>

Branch to (relative address or label) if condition(cc) is true

A) Conditional Transfer.

| (cc) | Name                     | Flag Conditions |

|------|--------------------------|-----------------|

| CC   | Carry clear .            | C = 0           |

| cs   | Carry set                | C = 1           |

| EQ   | Equal to (0)             | 2 = 1           |

| GE   | Greater than or equal to | и⊕v = 0         |

| GT   | Greater than             | (א⊕V) + Z = 0   |

| HI   | Higher than              | C + Z = 0       |

| LE   | Less than or equal to    | (N⊕V) + Z = 1   |

| LS   | than or the same as      | C + Z = 1       |

| LT   | Less than                | N ⊕ V = 1       |

| MI   | Minus, or negative       | N * 1           |

| NE   | Not equal to (0)         | z = 0           |

| PL   | Plus, or positive        | N = 0           |

| vc   | No overflow              | V = 0           |

| vs   | Result is too large      | V = 1           |

B) Uncorditional Transfer

JMP <relative address or label>

BRA <relative address or label>

Branch to (relative address or label) unconditionally

|           | Compare                    | Effect                | Restriction                                                |

|-----------|----------------------------|-----------------------|------------------------------------------------------------|

|           | CMP.size <s>, <d></d></s>  | ? = <d> - <s></s></d> | ( <d> = Di)</d>                                            |

| (Address) | CMPA.size <s>, <d></d></s> | ? = <d> - <s></s></d> | $( = Ai) (size \neq B)$                                    |

| •         | CMPI.size <s>, <d></d></s> | ? = <d> - <s></s></d> | $(\langle s \rangle = Imm) (\langle d \rangle \neq Ai)$    |

| •         | CMPM.size <s>, <d></d></s> | ? = <d> - <s></s></d> | (Both $\langle s \rangle$ and $\langle d \rangle = (Ai)+)$ |

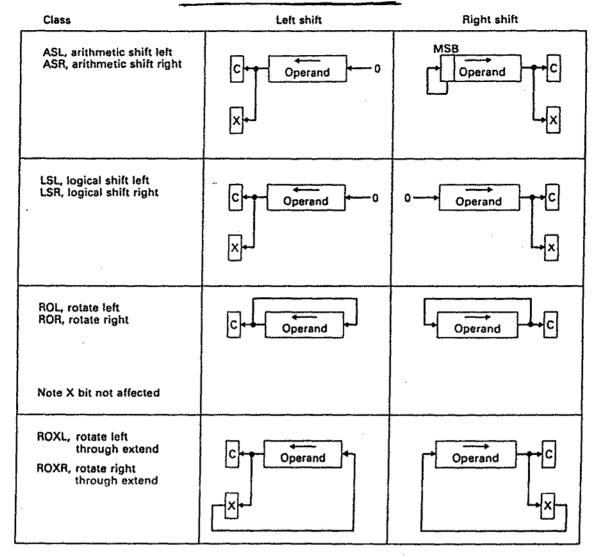

Arithmetic shifts update all bits of the CCR. The N and Z bits are set or cleared as we would expect. The V bit is set if the most significant bit of the operand is changed at any time during the shift operation. The C and X bits are set according to the last bit shifted out of the operand. However, if the shift count is zero, C is cleared and X is unaffected. Logical shifts and rotates clear the V bit.

#### Assembly Language Form of Shift Operations

All eight shift instructions are expressed in one of three ways. These are illustrated by the ASL (arithmetic shift left) instruction.

| Mode 1. | ASL Dx.Dy       | Shift Dy by Dx bits                   |

|---------|-----------------|---------------------------------------|

| Mode 2. | ASL # (data),Dy | Shift Dy by #data bits                |

| Mode 3. | ASL (ea)        | Shift the contents of ea by one place |

A shift instruction can be applied to a byte, word, or longword operand, with the exception of mode 3 shifts, which act only on words.

In mode 1, the "source" operand, Dx, specifies how many places the destination operand, Dy, needs to be shifted. Dy may be shifted by 1 to 32 bits. In mode 2, the literal, #(data), specifies how many places Dy needs to be shifted; this must be in the range 1 to 8. In mode 3, the memory location specified by the effective address, (ea), is shifted one place. Many microprocessors permit only the static shifts of modes 2 and 3. The 68000 permits dynamic shifts (i.e., mode 1) because the number of bits to be shifted is computed at run-time.

#### ASSEMBLER DIRECTIVES

(Allocate storage, Define constants, Link identifiers to values, control assembling)

DS

DC

EQU

A line starting at column 1 with an \* is a comment.

Any other line is composed of three parts:

- Label (starts at column 1 with a letter and consists of at most 8 characters)

- instruction or assembler directive

- Comment

(1st and 3rd parts are optional. If label is not used then column 1 is empty)

TTL (gives the title of the program)

identifier EQU value (links an identifier to a value)

ORG SHHHHHH (Origin of data)

identifier DS.size length (reserves memory space for variables)

identifier DC.size value (defines constants)

ORG \$HHHHHH (Origin of program)

INSTRUCTIONS ARE PLACED HERE

END (indicates the end of the program)

Given two vectors of 20 one-byte numbers each, a) located at addresses VECT1 and VECT2.

Add these vectors and put the resulting vector at address VECT2.

## AddVect:

| CLR.L   | D0        | 50 ←0      |

|---------|-----------|------------|

| MOVEA.L | VECT1, A0 | Ao WECT    |

| MOVEA.L | VECT2, A1 | A, L VECT2 |

Loop:

MOVE.B

$$(A0)+$$

, D1  $D_1 \leftarrow M[A_0]$ ;  $A_0 \leftarrow A_0+1$

ADD.B  $D1$ ,  $(A1)+$   $M[A_1] \leftarrow M[A_1]+D_1$ ;  $A_1 \leftarrow A_1+1$

ADDI.B #\$1, D0  $D_0 \leftarrow D_0+1$

CMPI.B #20, D0  $D_0-20$  (\$14)?

BNE Loop \$\frac{1}{2}\$ \$\frac{1}{2}\$ branch to Loop.

Done:

b) Given a vector of 10 one-byte numbers, located at address NUMBERS.

Find the sum (address SUM) and the average (address AVERAGE) of these numbers.

Stats:

CLR.L D0  $D_0 \leftarrow 0$  MOVE.B #10, D1  $D_1 \leftarrow 10$   $D_2 \leftarrow 0$  MOVEA.L NUMBERS, A0  $D_0 \leftarrow 0$  Numbers

Loop:

MOVE.B (A0)+, D2  $D_2 \leftarrow M[A_0]$ ;  $A_0 \leftarrow A_0 + 1$

ADD.L D2, D0  $D_0 \leftarrow D_0 + D_2$  SUBI.B #1, D1  $D_1 \leftarrow D_1 - 1$  BNE Loop 9 $f(D_1 \neq 0)$  branch to Loop

MOVE.W DO, SUM M[sum] <- Do

DIVU #\$A, D0  $D_0 \cdot W \leftarrow D_0 / 10$ MOVE.B D0, AVERAGE  $M[AVERAGE] \leftarrow D_0$

Done: